Розробка операційних пристроїв з плаваючою крапкою

DOI:

https://doi.org/10.15587/2706-5448.2023.290127Ключові слова:

помножувач з плаваючою крапкою, суперскалярний процесор, закон асоціативності, алгоритм Baugh-Wooley, CISC-RISCАнотація

В роботі показано відомий підхід до побудови ядер в багатоядерних мікропроцесорах, що ґрунтується на застосуванні моделі обчислень під керуванням графа потоку даних (data flow). Архітектура таких ядер ґрунтується на застосуванні моделі потоку даних на рівні скороченого набору команд, запропонованої Yale Patt. Об’єктом досліджень є модель обчислень на основі управління потоком даних у багатоядерному мікропроцесорі.

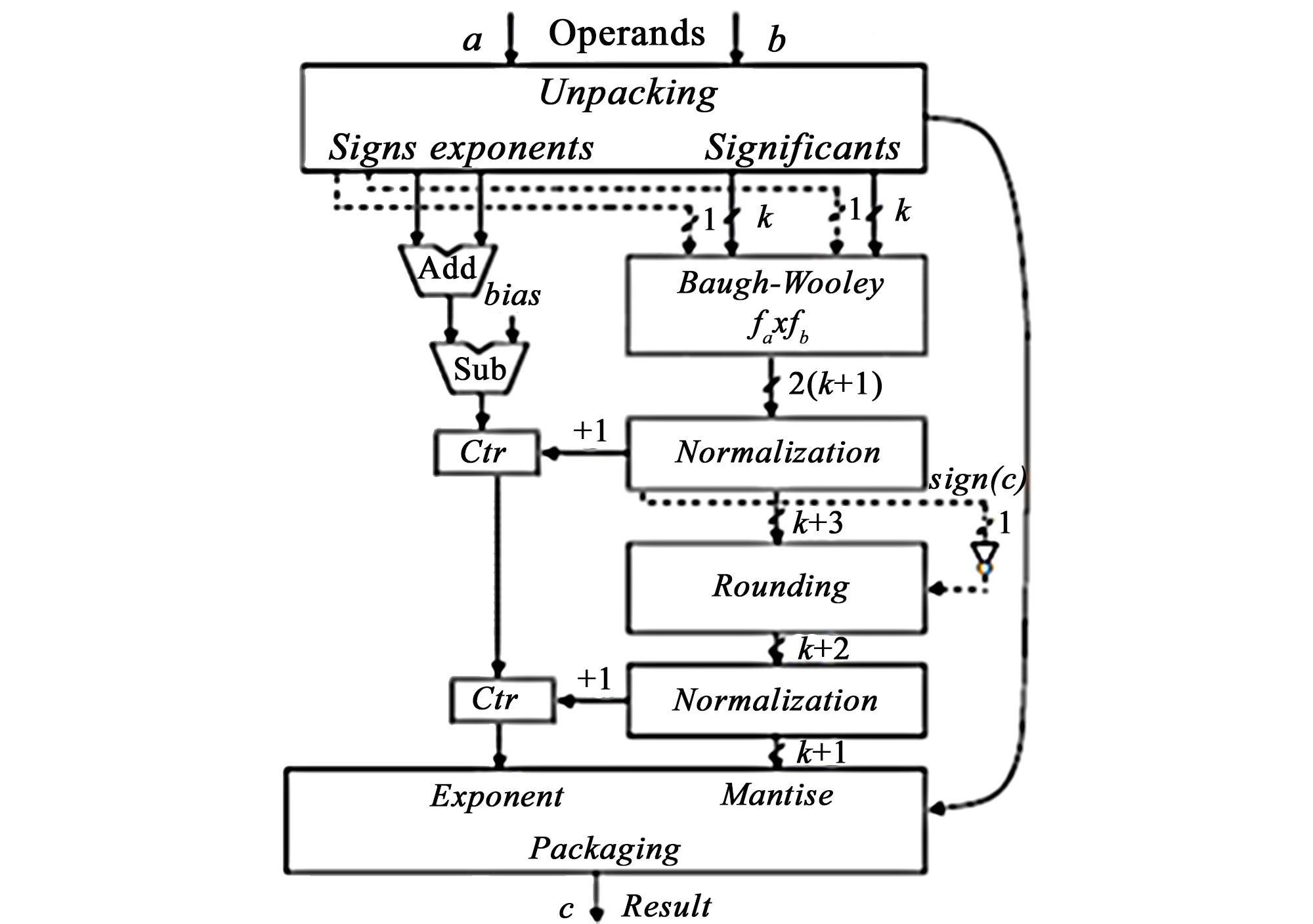

Представлені результати розробки помножувача з плаваючою крапкою, що може динамічно перестроюватися на обробку п’яти різних форматів операндів з плаваючою крапкою та підхід до побудови операційного пристрою додавання-віднімання послідовності чисел з плаваючою крапкою, для якого без додаткових програмних ускладнень виконується закон асоціативності. На основі розробленої схеми помножувача з плаваючою крапкою можливо реалізувати різні варіанти швидкодіючого помножувача як з фіксованою, так і з плаваючою крапкою, що можуть знайти комерційне застосування. Додавши в кожний із сегментів помножувача елементи пам’яті, можливо отримати варіанти побудови дуже швидкодіючих конвеєрних помножувачів. Схема помножувача має обмеження: доданок не обчислюється для денормалізованих операндів, але стандарт на обчислення з плаваючою крапкою не вимагає обов’язкової обробки денормалізованих операндів. В таких випадках помножувач, в якості результатів, упаковує нескінченість.

Впровадження між’ядерного операційного пристрою суматора-віднімача з плаваючою крапкою може розглядатися як новий підхід до практичного вирішення завдань динамічного планування при виконанні операцій додавання-віднімання в рамках багатоядерного мікропроцесора. Обмеження його впровадження пов’язані із великою кількістю апаратурних затрат, необхідних для реалізації. Для оцінки цієї складності проведена оцінка значення розрядностей основних його блоків для різних форматів представлення чисел з плаваючою крапкою, відповідно до стандарту на плаваючу крапку.

Посилання

- Patt, Y., Hwu, W. et al. (1986). Experiments with HPS, a Restricted Data Flow Micro architecture for High Performance Computers. COMPCON 86, 254–258.

- Simone, M., Essen, A., Ike, A., Krishnamoorthy, A., Maruyama, T., Patkar, N. et al. (1995). Implementation trade-offs in using a restricted data flow architecture in a high performance RISC microprocessor. ACM SIGARCH Computer Architecture News, 23 (2), 151–162. doi: https://doi.org/10.1145/225830.224411

- Hennessy, J. L., Patterson, D. A. (2019). Computer Architecture: A Cuantitative Approach. Morgan Kaufmann, 1527.

- Kanter, D. (2012). Intel’s Haswell CPU Microarchitecture. Available at: http://www.realworldtech.com/haswell-cpu/

- Shen, J., Lipasti, M. (2013). Modern Processor Design: Fundamentals of Superscalar Processors. Waveland Press, 642.

- Lutskyi, H. M., Dolholenko, O. M., Aksonenko, S. V., Storozhuk, V. O. (2014). Modeliuvannia obmezhenoi realizatsii arkhitektury potoku danykh v strukturi superskaliarnoho protsesora. Visnyk NTUU «KPI». Informatyka, upravlinnia ta obchysliuvalna tekhnika, 60, 83–94.

- Dolholenko, A. O., Yatsun, V. O. (2016). Realizatsiia operatsiinoho prystroiu sumatora/vidnimacha z plavaiuchoiu krapkoiu dlia yadra superskaliarnoho protsesora. Visnyk NTUU «KPI». Informatyka, upravlinnia ta obchysliuvalna tekhnika, 64, 106–116.

- IEEE 754: Standard for Binary Floating-Point Arithmetic (2019). Available at: https://grouper.ieee.org/groups/msc/ANSI_IEEE-Std-754-2019/background/

- What Every Computer Scientist Should Know About Floating-Point Arithmetic. Available at: https://ece.uwaterloo.ca/~dwharder/NumericalAnalysis/02Numerics/Double/paper.pdf

- Knut, D. (1977). Iskusstvo programmirovaniia dlia EVM. Vol. 2. Moscow: Mir, 724.

- Mak-Kraken, D., Dorn, U. (1977). Chislennye metody i programmirovanie na FORTRANE. Moscow: Mir, 584.

- Strictly, there exist other variants of compensated summation as well: see Higham, Nicholas (2002). Accuracy and Stability of Numerical Algorithms. SIAM, 110–123.

- Lutskyi, H. M. et al. (2016). Metody ta zasoby pidvyshchennia efektyvnosti rishennia zdach na osnovi perestroiuvanykh obchysliuvalnykh zasobiv na PLIS – Zakl. zvit po NDR No. DR 0216U007635. Kyiv, 244.

- Baugh, C. R., Wooley, B. A. (1973). A Two’s Complement Parallel Array Multiplication Algorithm. IEEE Transactions on Computers, C–22 (12), 1045–1047. doi: https://doi.org/10.1109/t-c.1973.223648

- Parhami, B. (2000). Computer Arithmetic. Algorithms and Hardware Designs. New York: Oxford University Press, 491.

##submission.downloads##

Опубліковано

Як цитувати

Номер

Розділ

Ліцензія

Авторське право (c) 2023 Georgi Luсkij, Oleksandr Dolholenko

Ця робота ліцензується відповідно до Creative Commons Attribution 4.0 International License.

Закріплення та умови передачі авторських прав (ідентифікація авторства) здійснюється у Ліцензійному договорі. Зокрема, автори залишають за собою право на авторство свого рукопису та передають журналу право першої публікації цієї роботи на умовах ліцензії Creative Commons CC BY. При цьому вони мають право укладати самостійно додаткові угоди, що стосуються неексклюзивного поширення роботи у тому вигляді, в якому вона була опублікована цим журналом, але за умови збереження посилання на першу публікацію статті в цьому журналі.