Design of improved structures for multi-bit data addition devices in binary codes of the Rademacher theoretical-numerical basis

DOI:

https://doi.org/10.15587/1729-4061.2025.347658Keywords:

cascade and pyramid adders, full and half adders, time and hardware complexity, FPGAAbstract

This study investigates the process of designing multi-bit adders based on an improved element base of their components in binary codes of Rademacher theoretical-numerical basis. The task addressed relates to the fact that the known element base of modern single-bit adders does not make it possible to achieve the minimax characteristics of sum formation and carry-save efficiency in their structures in 1 micro cycle.

The improved element base of single-bit adders has been built on the basis of the «Exclusive AND» logic element, which has low hardware complexity and high speed of output signal formation.

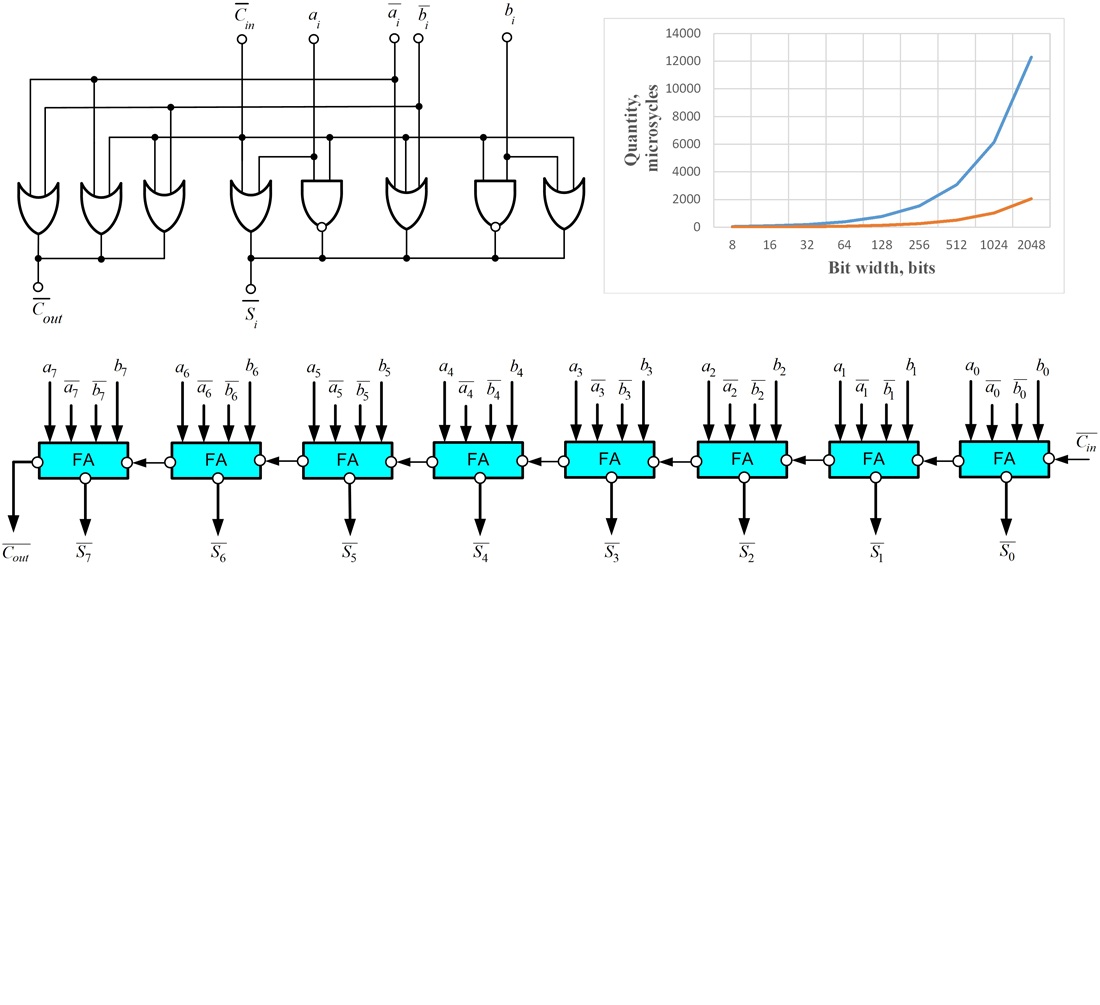

Improved architectural solutions for full and half single-bit binary adders with minimax characteristics of hardware and time complexity in structures of multi-bit adders of various types have been applied. The system characteristics of microelectronic structures of multi-bit adders of various types based on full and half single-bit binary combinational adders with direct, inverse, and paraphase inputs and outputs have been investigated.

As a result, it has been theoretically established and practically confirmed that multi-bit adders based on an improved element base have 2 times less hardware complexity and 6 times higher speed.

The structure of a cascaded n-bit fast adder has been designed, which has a speed 1.8 times higher than that of the known implementation.

Using the VHDL hardware description language and Vivado CAD, a 64-bit cascade adder was modelled and synthesized on FPGA, which has twice the speed of the known adder.

The designed multi-bit Rademacher basis adders are applicable to statistical, correlation, and entropy analysis tasks, video image processing, image recognition, as well as various artificial intelligence tasks

References

- Heath, R. W. (2017). Introduction to Wireless Digital Communication: A Signal Processing Perspective. Pearson, 464. Available at: https://www.pearson.com/en-us/subject-catalog/p/introduction-to-wireless-digital-communication-a-signal-processingperspective/P200000009126/9780134431796

- Allemang, R., Avitabile, P. (Eds.) (2022). Handbook of Experimental Structural Dynamics. Springer. https://doi.org/10.1007/978-1-4614-4547-0

- Anand Kumar, A. (2016). Fundamentals of Digital Circuits. PHI. Available at: https://books.google.co.in/books?id=CyavDAAAQBAJ&printsec=copyright#v=onepage&q&f=false

- Kusuma, H S., Kalpana, H. M., Ravi, H. K (2025). Design and Comparative Analysis of Half and Full Adders Using CMOS and Pass Transistor Logic Styles. 2025 3rd International Conference on Smart Systems for Applications in Electrical Sciences (ICSSES), 1–6. https://doi.org/10.1109/icsses64899.2025.11010034

- Kumar, P., Bhandari, N. S., Bhargav, L., Rathi, R.,Yadav, S. C. (2017). Design of low power and area efficient half adder using pass transistor and comparison of various performance parameters. 2017 International Conference on Computing, Communication and Automation (ICCCA), 1477–1482. https://doi.org/10.1109/ccaa.2017.8230033

- Nykolaichuka, Ya. M. (Ed.) (2017). Spetsializovani kompiuterni tekhnolohiyi v informatytsi. Ternopil: Beskydy, 913. Available at: https://scs.wunu.edu.ua/?p=353

- John, V., Sam, S., Radha, S., Paul, P. S., Samuel, J. (2020). Design of a power-efficient Kogge–Stone adder by exploring new OR gate in 45nm CMOS process. Circuit World, 46 (4), 257–269. https://doi.org/10.1108/cw-12-2018-0104

- Yadav, R., Sura, A., Dahiya, S. (2021). Half adder design using various technologies and comparison of. International Journal of Engineering Applied Sciences and Technology, 6 (2). https://doi.org/10.33564/ijeast.2021.v06i02.016

- Jhamb, Dr. M., Kumar, M., Vishal (2020). Full Adder for Low Power Applications. International Journal of Innovative Technology and Exploring Engineering, 9 (4), 2612–2687. https://doi.org/10.35940/ijitee.d1846.029420

- Hameed, A. S., Kathem, M. J. (2021). High speed modified carry save adder using a structure of multiplexers. International Journal of Electrical and Computer Engineering (IJECE), 11 (2), 1591. https://doi.org/10.11591/ijece.v11i2.pp1591-1598

- Davletova, A. Ya., Nykolaichuk, Ya. M. (2017). Pat. No. 115861 UA. Odnorozriadnyi nepovni sumator. No. u201612463; declareted: 07.12.2016, published: 25.04.2017. Available at: https://sis.nipo.gov.ua/uk/search/detail/805118/

- Hryha, V., Dzundza, B., Melnychuk, S., Manuliak, I., Terletsky, A., Deichakivskyi, M. (2023). Design of various operating devices for sorting binary data. Eastern-European Journal of Enterprise Technologies, 4 (4 (124)), 6–18. https://doi.org/10.15587/1729-4061.2023.285997

- Dunets, R., Gryga, V. (2015). Spatio-temporal synthesis of transformation matrix of reverse fast cosine transformation. The Experience of Designing and Application of CAD Systems in Microelectronics, 45–49. https://doi.org/10.1109/cadsm.2015.7230792

- Gryga, V., Kolosov, I., Danyluk, O. (2016). The development of a fast iterative algorithm structure of cosine transform. 2016 13th International Conference on Modern Problems of Radio Engineering, Telecommunications and Computer Science (TCSET), 506–509. https://doi.org/10.1109/tcset.2016.7452100

- Gryga, V., Dzundza, B., Dadiak, I., Nykolaichuk, Y. (2018). Research and implementation of hardware algorithms for multiplying binary numbers. 2018 14th International Conference on Advanced Trends in Radioelecrtronics, Telecommunications and Computer Engineering (TCSET), 1277–1281. https://doi.org/10.1109/tcset.2018.8336427

- Nykolaichuk, Ya. M., Hryha, V. M., Nykolaichuk, L. M., Pitukh, I. R. (2021). Pat. No. 147277 UA. Povnyi odnorozriadnyi sumator. No. a202006409; declareted: 05.10.2020, published: 06.04.2022. Available at: https://sis.nipo.gov.ua/en/search/detail/1457390/

- Nykolaichuk, Ya. M. (2023). Pat. No. 153527 UA. Povnyi odnorozriadnyi sumator. No. u202203361; declareted: 13.09.2022, published: 19.07.2023. Available at: https://sis.nipo.gov.ua/en/search/detail/1748918/

- Nykolaichuk, Ya. M. (2023). Pat. No. 150331 UA. Sumator z pryskorenym perenosom. No. u202104275; declareted: 21.07.2021, published: 02.02.2022. Available at: https://sis.nipo.gov.ua/en/search/detail/1676002/

- Li, H., Ye, W. (2016). Efficient implementation of FPGA based on Vivado High Level Synthesis. 2016 2nd IEEE International Conference on Computer and Communications (ICCC), 2810–2813. https://doi.org/10.1109/compcomm.2016.7925210

Downloads

Published

How to Cite

Issue

Section

License

Copyright (c) 2025 Yaroslav Nykolaychuk, Igor Pitukh, Volodymyr Hryha

This work is licensed under a Creative Commons Attribution 4.0 International License.

The consolidation and conditions for the transfer of copyright (identification of authorship) is carried out in the License Agreement. In particular, the authors reserve the right to the authorship of their manuscript and transfer the first publication of this work to the journal under the terms of the Creative Commons CC BY license. At the same time, they have the right to conclude on their own additional agreements concerning the non-exclusive distribution of the work in the form in which it was published by this journal, but provided that the link to the first publication of the article in this journal is preserved.

A license agreement is a document in which the author warrants that he/she owns all copyright for the work (manuscript, article, etc.).

The authors, signing the License Agreement with TECHNOLOGY CENTER PC, have all rights to the further use of their work, provided that they link to our edition in which the work was published.

According to the terms of the License Agreement, the Publisher TECHNOLOGY CENTER PC does not take away your copyrights and receives permission from the authors to use and dissemination of the publication through the world's scientific resources (own electronic resources, scientometric databases, repositories, libraries, etc.).

In the absence of a signed License Agreement or in the absence of this agreement of identifiers allowing to identify the identity of the author, the editors have no right to work with the manuscript.

It is important to remember that there is another type of agreement between authors and publishers – when copyright is transferred from the authors to the publisher. In this case, the authors lose ownership of their work and may not use it in any way.