Розроблення удосконалених структур багаторозрядних пристроїв сумування даних у двійкових кодах теоретико-числового базису Радемахера

DOI:

https://doi.org/10.15587/1729-4061.2025.347658Ключові слова:

каскадні та пірамідальні суматори, повні та неповні суматори, часова та апаратна складність, ПЛІСАнотація

Об’єктом дослідження є процес проєктування багаторозрядних суматорів на основі удосконаленої елементної бази їх компонентів у двійкових кодах теоретико-числового базису Радемахера.

Проблемою даного дослідження є те, що відома елементна база сучасних однорозрядних суматорів не дозволяє досягти мінімаксних характеристик формування суми і наскрізного переносу у їх структурах за 1 мікротакт.

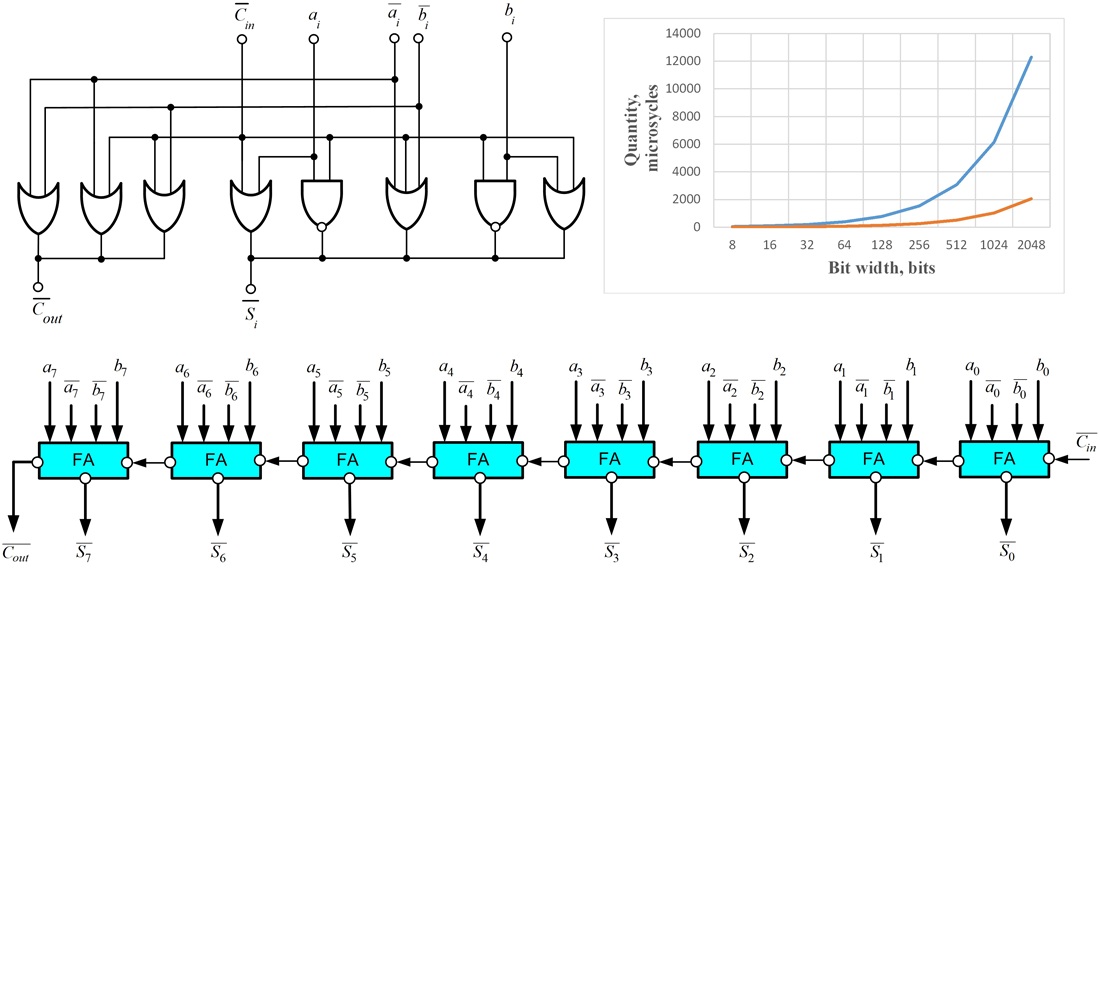

Удосконалена елементна база однорозрядних суматорів побудована на базі логічного елемента «Виключне І», який має низьку апаратну складність та високу швидкодію формування вихідних сигналів.

Застосовано удосконалені архітектурні рішення повних та неповних однорозрядних двійкових суматорів з мінімаксними характеристиками апаратної та часової складності у структурах багаторозрядних суматорів різних типів. Досліджено системні характеристики мікроелектронних структур багаторозрядних суматорів різних типів на базі повних та неповних однорозрядних двійкових комбінаційних суматорів з прямими, інверсними та парафазними входо-виходами.

Розроблено структуру каскадного n-розрядного суматора з прискореним переносом, який має швидкодію в 1,8 рази більшою у порівнянні з відомою реалізацією.

В результаті теоретично встановлено та практично підтверджено, що багаторозрядні суматори на удосконаленій елементній базі мають у 2 рази меншу апаратну складність та у 6 разів більшу швидкодію.

Розроблено структуру каскадного n-розрядного суматора з прискореним переносом, який має швидкодію в 1,8 рази більшою у порівнянні з відомою реалізацією.

З використанням мови опису апаратних засобів VHDL та САПР Vivado проведено моделювання та синтез на ПЛІС 64-бітного суматора каскадного типу, який має у 2 рази більшу швидкодію у порівнянні з відомим.

Сферою застосування розроблених багаторозрядних суматорів базису Радемахера є задачі статистичного, кореляційного, ентропійного аналізу, опрацювання відеозображень, розпізнавання образів та вирішення різноманітних завдань штучного інтелекту

Посилання

- Heath, R. W. (2017). Introduction to Wireless Digital Communication: A Signal Processing Perspective. Pearson, 464. Available at: https://www.pearson.com/en-us/subject-catalog/p/introduction-to-wireless-digital-communication-a-signal-processingperspective/P200000009126/9780134431796

- Allemang, R., Avitabile, P. (Eds.) (2022). Handbook of Experimental Structural Dynamics. Springer. https://doi.org/10.1007/978-1-4614-4547-0

- Anand Kumar, A. (2016). Fundamentals of Digital Circuits. PHI. Available at: https://books.google.co.in/books?id=CyavDAAAQBAJ&printsec=copyright#v=onepage&q&f=false

- Kusuma, H S., Kalpana, H. M., Ravi, H. K (2025). Design and Comparative Analysis of Half and Full Adders Using CMOS and Pass Transistor Logic Styles. 2025 3rd International Conference on Smart Systems for Applications in Electrical Sciences (ICSSES), 1–6. https://doi.org/10.1109/icsses64899.2025.11010034

- Kumar, P., Bhandari, N. S., Bhargav, L., Rathi, R.,Yadav, S. C. (2017). Design of low power and area efficient half adder using pass transistor and comparison of various performance parameters. 2017 International Conference on Computing, Communication and Automation (ICCCA), 1477–1482. https://doi.org/10.1109/ccaa.2017.8230033

- Nykolaichuka, Ya. M. (Ed.) (2017). Spetsializovani kompiuterni tekhnolohiyi v informatytsi. Ternopil: Beskydy, 913. Available at: https://scs.wunu.edu.ua/?p=353

- John, V., Sam, S., Radha, S., Paul, P. S., Samuel, J. (2020). Design of a power-efficient Kogge–Stone adder by exploring new OR gate in 45nm CMOS process. Circuit World, 46 (4), 257–269. https://doi.org/10.1108/cw-12-2018-0104

- Yadav, R., Sura, A., Dahiya, S. (2021). Half adder design using various technologies and comparison of. International Journal of Engineering Applied Sciences and Technology, 6 (2). https://doi.org/10.33564/ijeast.2021.v06i02.016

- Jhamb, Dr. M., Kumar, M., Vishal (2020). Full Adder for Low Power Applications. International Journal of Innovative Technology and Exploring Engineering, 9 (4), 2612–2687. https://doi.org/10.35940/ijitee.d1846.029420

- Hameed, A. S., Kathem, M. J. (2021). High speed modified carry save adder using a structure of multiplexers. International Journal of Electrical and Computer Engineering (IJECE), 11 (2), 1591. https://doi.org/10.11591/ijece.v11i2.pp1591-1598

- Davletova, A. Ya., Nykolaichuk, Ya. M. (2017). Pat. No. 115861 UA. Odnorozriadnyi nepovni sumator. No. u201612463; declareted: 07.12.2016, published: 25.04.2017. Available at: https://sis.nipo.gov.ua/uk/search/detail/805118/

- Hryha, V., Dzundza, B., Melnychuk, S., Manuliak, I., Terletsky, A., Deichakivskyi, M. (2023). Design of various operating devices for sorting binary data. Eastern-European Journal of Enterprise Technologies, 4 (4 (124)), 6–18. https://doi.org/10.15587/1729-4061.2023.285997

- Dunets, R., Gryga, V. (2015). Spatio-temporal synthesis of transformation matrix of reverse fast cosine transformation. The Experience of Designing and Application of CAD Systems in Microelectronics, 45–49. https://doi.org/10.1109/cadsm.2015.7230792

- Gryga, V., Kolosov, I., Danyluk, O. (2016). The development of a fast iterative algorithm structure of cosine transform. 2016 13th International Conference on Modern Problems of Radio Engineering, Telecommunications and Computer Science (TCSET), 506–509. https://doi.org/10.1109/tcset.2016.7452100

- Gryga, V., Dzundza, B., Dadiak, I., Nykolaichuk, Y. (2018). Research and implementation of hardware algorithms for multiplying binary numbers. 2018 14th International Conference on Advanced Trends in Radioelecrtronics, Telecommunications and Computer Engineering (TCSET), 1277–1281. https://doi.org/10.1109/tcset.2018.8336427

- Nykolaichuk, Ya. M., Hryha, V. M., Nykolaichuk, L. M., Pitukh, I. R. (2021). Pat. No. 147277 UA. Povnyi odnorozriadnyi sumator. No. a202006409; declareted: 05.10.2020, published: 06.04.2022. Available at: https://sis.nipo.gov.ua/en/search/detail/1457390/

- Nykolaichuk, Ya. M. (2023). Pat. No. 153527 UA. Povnyi odnorozriadnyi sumator. No. u202203361; declareted: 13.09.2022, published: 19.07.2023. Available at: https://sis.nipo.gov.ua/en/search/detail/1748918/

- Nykolaichuk, Ya. M. (2023). Pat. No. 150331 UA. Sumator z pryskorenym perenosom. No. u202104275; declareted: 21.07.2021, published: 02.02.2022. Available at: https://sis.nipo.gov.ua/en/search/detail/1676002/

- Li, H., Ye, W. (2016). Efficient implementation of FPGA based on Vivado High Level Synthesis. 2016 2nd IEEE International Conference on Computer and Communications (ICCC), 2810–2813. https://doi.org/10.1109/compcomm.2016.7925210

##submission.downloads##

Опубліковано

Як цитувати

Номер

Розділ

Ліцензія

Авторське право (c) 2025 Yaroslav Nykolaychuk, Igor Pitukh, Volodymyr Hryha

Ця робота ліцензується відповідно до Creative Commons Attribution 4.0 International License.

Закріплення та умови передачі авторських прав (ідентифікація авторства) здійснюється у Ліцензійному договорі. Зокрема, автори залишають за собою право на авторство свого рукопису та передають журналу право першої публікації цієї роботи на умовах ліцензії Creative Commons CC BY. При цьому вони мають право укладати самостійно додаткові угоди, що стосуються неексклюзивного поширення роботи у тому вигляді, в якому вона була опублікована цим журналом, але за умови збереження посилання на першу публікацію статті в цьому журналі.

Ліцензійний договір – це документ, в якому автор гарантує, що володіє усіма авторськими правами на твір (рукопис, статтю, тощо).

Автори, підписуючи Ліцензійний договір з ПП «ТЕХНОЛОГІЧНИЙ ЦЕНТР», мають усі права на подальше використання свого твору за умови посилання на наше видання, в якому твір опублікований. Відповідно до умов Ліцензійного договору, Видавець ПП «ТЕХНОЛОГІЧНИЙ ЦЕНТР» не забирає ваші авторські права та отримує від авторів дозвіл на використання та розповсюдження публікації через світові наукові ресурси (власні електронні ресурси, наукометричні бази даних, репозитарії, бібліотеки тощо).

За відсутності підписаного Ліцензійного договору або за відсутністю вказаних в цьому договорі ідентифікаторів, що дають змогу ідентифікувати особу автора, редакція не має права працювати з рукописом.

Важливо пам’ятати, що існує і інший тип угоди між авторами та видавцями – коли авторські права передаються від авторів до видавця. В такому разі автори втрачають права власності на свій твір та не можуть його використовувати в будь-який спосіб.