Синтез нейроелементів рекурсивного типу з паралельною вертикально-груповою обробкою даних

DOI:

https://doi.org/10.15587/1729-4061.2025.329139Ключові слова:

модель нейроелемента, реальний час виконання обчислень, апаратна реалізація нейронного елементаАнотація

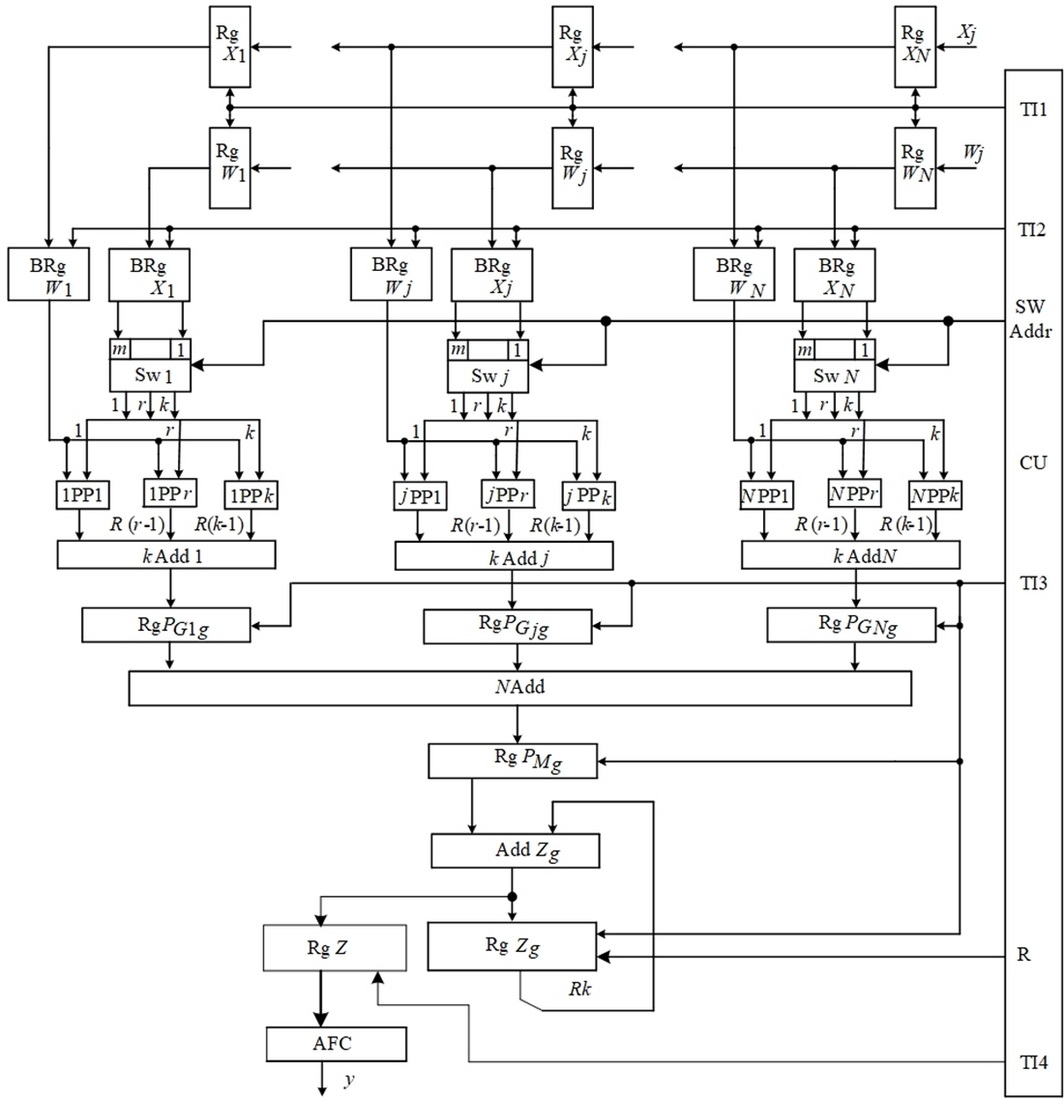

Об’єктом дослідження є процеси паралельного вертикально-групового опрацювання даних та мінімізації витрат обладнання, що забезпечують синтез нейронних елементів рекурсивного типу реального часу з високою ефективністю використання обладнання. Розроблено модель нейроелемента рекурсивного типу, яка за рахунок використання паралельного вертикально-групового методу обчислення скалярного добутку та можливості вибору кількості розрядів у групі для формування часткових добутків узгоджує час надходження вагових коефіцієнтів і вхідних даних з часом обчислення результату на виході нейроелемента. Такий підхід забезпечує апаратну реалізацію нейронного елемента з мінімізацією використання обладнання. Розроблено базову структуру нейроелемента, яка за рахунок використання апаратного відображення розробленої графової моделі, регулярності і модульності структури забезпечує синтез апаратних засобів для конкретного застосування. Використання конвеєризації і просторового паралелізму обробки даних, організації процесу обчислення скалярного добутку як виконання єдиної операції забезпечує реалізацію нейроелемента для роботи у реальному часі. Розроблено аналітичні вирази для оцінювання параметрів нейроелемента в залежності від розрядності операндів, кількості вхідних даних та кількості розрядів у групі. Розроблено метод синтезу нейроелемента рекурсивного типу, який за рахунок використання базової структури, механізмів узгодження часу надходження вагових коефіцієнтів і вхідних даних з часом обчислення виходу забезпечує його реалізацію для конкретних застосувань. Врахування шляхів мінімізації витрат обладнання забезпечує створення нейроелемента з мінімальними апаратними затратами. Синтезований нейроелемент для розрядності даних 16 біт при збільшенні кількості розрядів, які одночасно обробляються у групі, з 2 до 8, забезпечує зменшення тривалості обробки у 2,8 разів при зниженні ефективності використання обладнання нейроелемента не більше як у 1,6 разів

Посилання

- Leigh, A. J., Heidarpur, M., Mirhassani, M. (2022). A Low-Resource Digital Implementation of the Fitzhugh-Nagumo Neuron. 2022 17th Conference on Ph.D Research in Microelectronics and Electronics (PRIME), 369–372. https://doi.org/10.1109/prime55000.2022.9816797

- Renteria-Cedano, J., Rivera, J., Sandoval-Ibarra, F., Ortega-Cisneros, S., Loo-Yau, R. (2019). SoC Design Based on a FPGA for a Configurable Neural Network Trained by Means of an EKF. Electronics, 8 (7), 761. https://doi.org/10.3390/electronics8070761

- Tsmots, I. G., Opotyak, Yu. V., Shtohrinets, B. V., Mamchur, T. B., Oliinyk, O. O. (2024). Operational basis of artificial neural networks and evaluation of hardware characteristics for its implementation. Ukrainian Journal of Information Technology, 6 (2), 125–138. https://doi.org/10.23939/ujit2024.02.125

- Kundu, S., Banerjee, S., Raha, A., Basu, K. (2022). Special Session: Effective In-field Testing of Deep Neural Network Hardware Accelerators. 2022 IEEE 40th VLSI Test Symposium (VTS), 1–4. https://doi.org/10.1109/vts52500.2021.9794227

- Wu, J., Zhao, B., Wen, H., Zhao, Q. (2022). Design of Neural Network Accelerator Based on In-Memory Computing Theory. 2022 4th International Conference on Natural Language Processing (ICNLP), 547–551. https://doi.org/10.1109/icnlp55136.2022.00100

- Sarg, M., Khalil, A. H., Mostafa, H. (2021). Efficient HLS Implementation for Convolutional Neural Networks Accelerator on an SoC. 2021 International Conference on Microelectronics (ICM), 1–4. https://doi.org/10.1109/icm52667.2021.9664920

- Nouacer, R., Hussein, M., Espinoza, H., Ouhammou, Y., Ladeira, M., Castiñeira, R. (2020). Towards a framework of key technologies for drones. Microprocessors and Microsystems, 77, 103142. https://doi.org/10.1016/j.micpro.2020.103142

- Saini, S., Lata, K., Sinha, G. R. (2021). VLSI and Hardware Implementations Using Modern Machine Learning Methods. CRC Press. https://doi.org/10.1201/9781003201038

- Davies, M., Srinivasa, N., Lin, T.-H., Chinya, G., Cao, Y., Choday, S. H. et al. (2018). Loihi: A Neuromorphic Manycore Processor with On-Chip Learning. IEEE Micro, 38 (1), 82–99. https://doi.org/10.1109/mm.2018.112130359

- Hager, G., Wellein, G. (2010). Introduction to High Performance Computing for Scientists and Engineers. CRC Press. https://doi.org/10.1201/ebk1439811924

- Tsmots, I., Teslyuk, V., Kryvinska, N., Skorokhoda, O., Kazymyra, I. (2022). Development of a generalized model for parallel-streaming neural element and structures for scalar product calculation devices. The Journal of Supercomputing, 79 (5), 4820–4846. https://doi.org/10.1007/s11227-022-04838-0

- Liu, W., Wang, Z., Liu, X., Zeng, N., Liu, Y., Alsaadi, F. E. (2017). A survey of deep neural network architectures and their applications. Neurocomputing, 234, 11–26. https://doi.org/10.1016/j.neucom.2016.12.038

- Tsmots, I. G., Opotyak, Y. V., Shtohrinets, B. V., Mamchur, T. B., Holubets, V. M. (2024). Model, structure and synthesis method of matrix-type neural element. Scientific Bulletin of UNFU, 34 (4), 68–77. https://doi.org/10.36930/40340409

- Tsmots, I., Skorokhoda, O., Ignatyev, I., Rabyk, V. (2017). Basic vertical-parallel real time neural network components. 2017 12th International Scientific and Technical Conference on Computer Sciences and Information Technologies (CSIT), 344–347. https://doi.org/10.1109/stc-csit.2017.8098801

- Leigh, A. J., Mirhassani, M., Muscedere, R. (2020). An Efficient Spiking Neuron Hardware System Based on the Hardware-Oriented Modified Izhikevich Neuron (HOMIN) Model. IEEE Transactions on Circuits and Systems II: Express Briefs, 67 (12), 3377–3381. https://doi.org/10.1109/tcsii.2020.2984932

- Pi, X., Lin, X. (2022). An FPGA-based Piecewise Linear Spiking Neuron for Simulating Bursting Behavior. 2022 IEEE 12th Annual Computing and Communication Workshop and Conference (CCWC), 0415–0420. https://doi.org/10.1109/ccwc54503.2022.9720886

- Wang, G., Fu, D. (2024). Spike Neural Network with Delayed Propagation Characteristics and Hardware Implementation. 2024 6th International Conference on Electronic Engineering and Informatics (EEI), 1181–1185. https://doi.org/10.1109/eei63073.2024.10696338

- Ramirez-Morales, R. R., Ponce-Ponce, V. H., Molina-Lozano, H., Sossa-Azuela, H., Islas-García, O., Rubio-Espino, E. (2024). Analog Implementation of a Spiking Neuron with Memristive Synapses for Deep Learning Processing. Mathematics, 12 (13), 2025. https://doi.org/10.3390/math12132025

- Xu, Q., Ding, S., Bao, H., Chen, M., Bao, B. (2022). Piecewise-Linear Simplification for Adaptive Synaptic Neuron Model. IEEE Transactions on Circuits and Systems II: Express Briefs, 69 (3), 1832–1836. https://doi.org/10.1109/tcsii.2021.3124666

- Bao, B., Zhu, Y., Li, C., Bao, H., Xu, Q. (2020). Global multistability and analog circuit implementation of an adapting synapse-based neuron model. Nonlinear Dynamics, 101 (2), 1105–1118. https://doi.org/10.1007/s11071-020-05831-z

- Tsmots, I. H., Shtohrinets, B. V., Kazymyra, I. Y., Lytvyn, A. A. (2023). Model and method for synthesis of neural element of parallel-streaming type. Scientific Bulletin of UNFU, 33 (2), 92–100. https://doi.org/10.36930/40330213

- Tsmots, I. H., Skorokhoda, O. V., Medykovskyi, M. O. (2017). Pat. No. 118596 UA. Prystriy dlia obchyslennia skaliarnoho dobutku. No. a201700835; declareted: 30.01.2017; declareted: 11.02.2019.

- Tsmots, I. H., Tesliuk, V. M., Lukashchuk, Yu. A., Kazymyra, I. Ya. (2021). Pat. No. 127774 UA. Prystriy dlia obchyslennia skaliarnoho dobutku. No. a202104653; declareted: 12.08.2021; declareted: 28.12.2023.

- Shymkovych, V., Doroshenko, A., Mamedov, T., Yatsenko, O. (2022) Automated design of an artificial neuron for field-programmable gate arrays based on an Algebra-Algorithmic approach. International Scientific Technical Journal "Problems of Control and Informatics", 67 (5), 61–72. https://doi.org/10.34229/2786-6505-2022-5-6

- Tsmots, I., Opotyak, Y., Shtohrinets, B. (2023). Method of Synthesis of Devices for Parallel Stream Calculation of Scalar Product in Real Time. Vìsnik Nacìonalʹnogo Unìversitetu “Lʹvìvsʹka Polìtehnìka”. Serìâ Ìnformacìjnì Sistemi Ta Merežì, 14, 248–266. https://doi.org/10.23939/sisn2023.14.248

- Lin, X., Lu, H., Pi, X., Wang, X. (2020). An FPGA-based Implementation Method for Quadratic Spiking Neuron Model. 2020 11th IEEE Annual Ubiquitous Computing, Electronics & Mobile Communication Conference (UEMCON), 0621–0627. https://doi.org/10.1109/uemcon51285.2020.9298029

- Zi, H., Zhao, K., Zhang, W. (2024). Designing and Accelerating Spiking Neural Network Based on High-Level Synthesis. 2024 Conference of Science and Technology for Integrated Circuits (CSTIC), 1–3. https://doi.org/10.1109/cstic61820.2024.10531920

- Hassantabar, S., Wang, Z., Jha, N. K. (2022). SCANN: Synthesis of Compact and Accurate Neural Networks. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 41 (9), 3012–3025. https://doi.org/10.1109/tcad.2021.3116470

##submission.downloads##

Опубліковано

Як цитувати

Номер

Розділ

Ліцензія

Авторське право (c) 2025 Ivan Tsmots, Vasyl Teslyuk, Yurii Opotyak, Taras Mamchur, Oleksandr Oliinyk

Ця робота ліцензується відповідно до Creative Commons Attribution 4.0 International License.

Закріплення та умови передачі авторських прав (ідентифікація авторства) здійснюється у Ліцензійному договорі. Зокрема, автори залишають за собою право на авторство свого рукопису та передають журналу право першої публікації цієї роботи на умовах ліцензії Creative Commons CC BY. При цьому вони мають право укладати самостійно додаткові угоди, що стосуються неексклюзивного поширення роботи у тому вигляді, в якому вона була опублікована цим журналом, але за умови збереження посилання на першу публікацію статті в цьому журналі.

Ліцензійний договір – це документ, в якому автор гарантує, що володіє усіма авторськими правами на твір (рукопис, статтю, тощо).

Автори, підписуючи Ліцензійний договір з ПП «ТЕХНОЛОГІЧНИЙ ЦЕНТР», мають усі права на подальше використання свого твору за умови посилання на наше видання, в якому твір опублікований. Відповідно до умов Ліцензійного договору, Видавець ПП «ТЕХНОЛОГІЧНИЙ ЦЕНТР» не забирає ваші авторські права та отримує від авторів дозвіл на використання та розповсюдження публікації через світові наукові ресурси (власні електронні ресурси, наукометричні бази даних, репозитарії, бібліотеки тощо).

За відсутності підписаного Ліцензійного договору або за відсутністю вказаних в цьому договорі ідентифікаторів, що дають змогу ідентифікувати особу автора, редакція не має права працювати з рукописом.

Важливо пам’ятати, що існує і інший тип угоди між авторами та видавцями – коли авторські права передаються від авторів до видавця. В такому разі автори втрачають права власності на свій твір та не можуть його використовувати в будь-який спосіб.